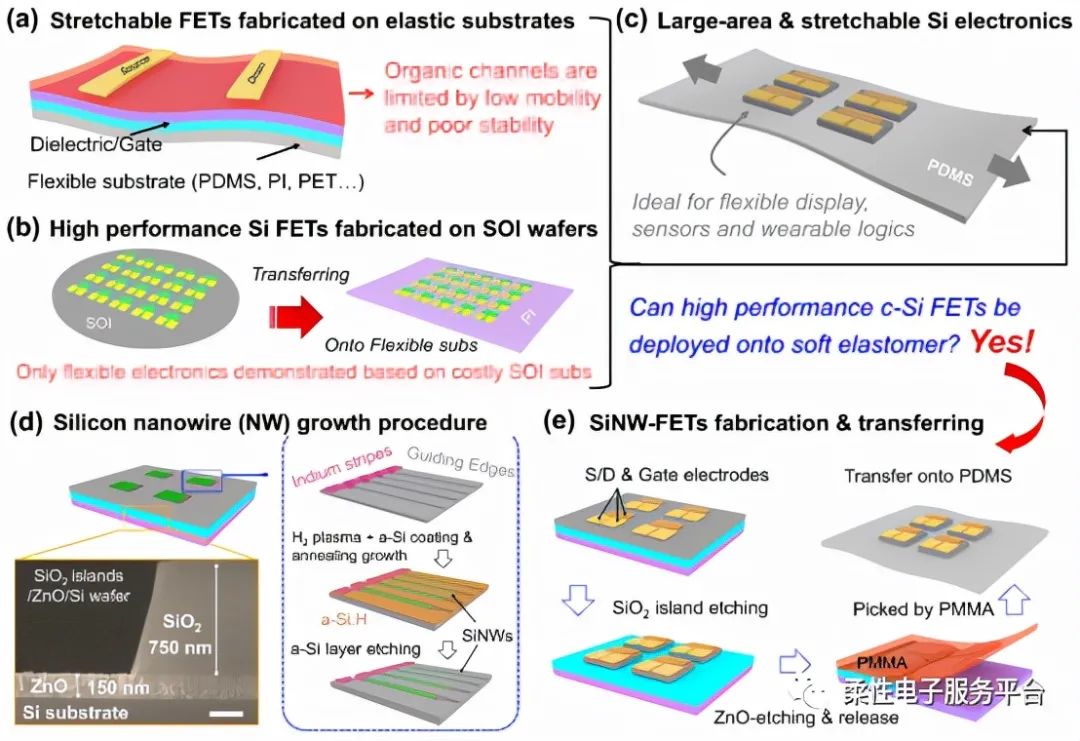

在大面积超柔性聚合物衬底上规模集成高性能硅基电子器件是实现新一代可拉伸柔性电子皮肤逻辑、传感和显示应用的关键技术难点。尽管柔性有机薄膜已被广泛用于可拉伸FET器件,但其相对较低的载流子迁移率和较差的器件稳定性限制了其规模化器件应用。此外,无机一维纳米线沟道材料具有高迁移率、低成本等优势,可用于开发各种高性能、低功耗柔性电子逻辑和超灵敏的场效应探测器件,但往往难以精确可控地实现规模集成应用。迄今为止,除了将SOI衬底上制备的晶硅逻辑规模转移到柔性PI衬底上外,还没有在高弹性PDMS衬底上实现大面积电子兼容的高性能可拉伸柔性晶硅电子器件制备和验证。

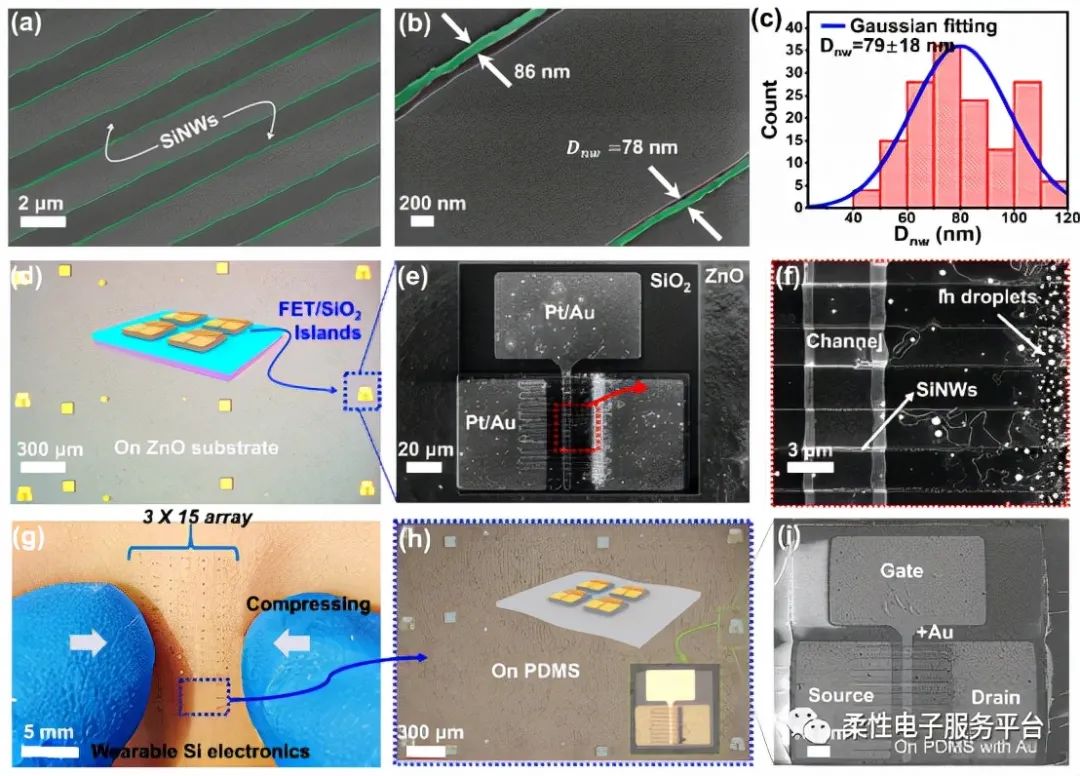

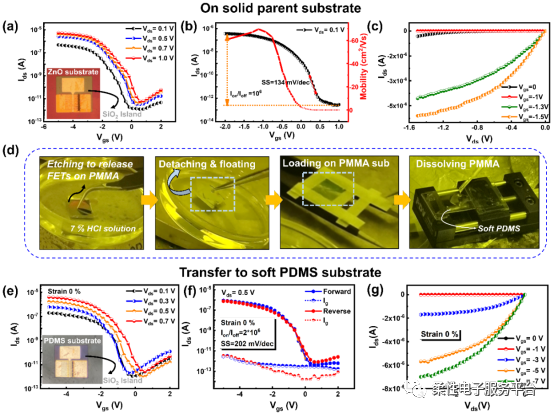

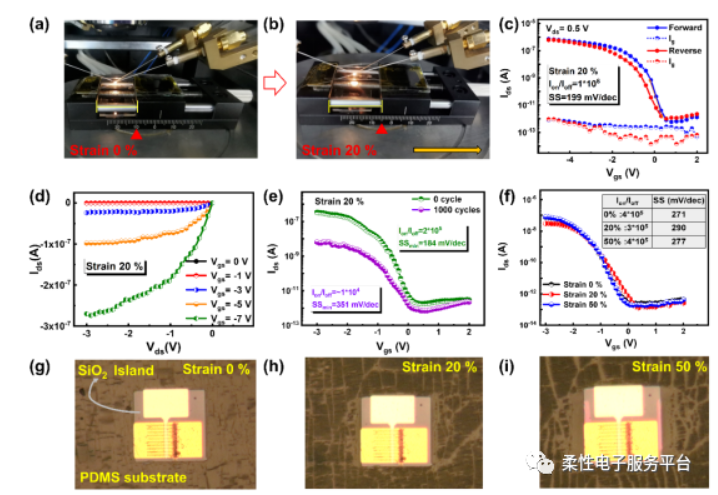

针对此需求,南京大学余林蔚、徐骏教授团队探索将高品质的一维硅纳米线(SiNWs)阵列可靠转移集成到弹性衬底PDMS之上,实现了超可拉伸的高性能场效应晶体管(FET)器件应用。基于课题组自组创新(见附录)的(In-plane solid-liquid-solid, IPSLS)生长模式,首先制备了规则有序的超细晶硅纳米线(直径<80 nm)沟道,再将其可靠批量转移到柔性PDMS衬底上。在优化设计的离散硬岛结构保护下,晶硅纳米线FET器件可以承受高达50 %的拉伸应变和超过1000个循环的重复拉伸测试(20 %应变下),其空穴载流子迁移率、电流开关比Ion/Ioff和亚阈值摆幅(SS)分别为~70 cm2 V−1 s−1,>105和134-277 mV/dec。这为探索和实现更先进的可拉伸电子皮肤、超柔性和非平面显示驱动(TFT)逻辑和生物传感/激励应用提供了理想可靠的高性能驱动逻辑器件基础!

图1:通过“硬岛”保护策略在PDMS衬底上可靠集成制备可拉伸c-Si FET电子器件结构

图2:台阶引导SiNWs的形貌表征及直接统计分布;晶圆衬底、人体皮肤及PDMS衬底上的SiNW-FET/硬岛器件结构

FET/硬岛器件在晶圆衬底上的电学性能测试及转移到弹性PDMS衬底上的制备流程和转移后电学性能测试

图4:SiNW-FET/硬岛器件拉伸不同比例实物图及拉伸后相应电性能测试;拉伸20 %重复1000次循环后电学性能展示